#### 8th International Conference on

"Technical and Physical Problems of Power Engineering"

5-7 September 2012

# Ostfold University College Fredrikstad, Norway

**ICTPE Conference**

www.iotpe.com

ictpe@iotpe.com ictpe0@gmail.com

Pages 359-363

ICTPE-2012 Number 75 Code 06PEL01

# IMPROVED SHORT CHANNEL EFFECTS IN 4H-SIC MOSFET WITH DUAL MATERIAL GATE STRUCTURE

M.A. Moradian <sup>1</sup> S.E. Hosseini <sup>2</sup>

Electrical Engineering Department, Hakim Sabzevari University of Sabzevar, Sabzevar, Iran mohammadali.moradian@yahoo.com

Electrical Engineering Department, Ferdowsi University of Mashhad, Mashhad, Iran e\_hosseini\_98@yahoo.com

Abstract- A dual material gate structure for a 4H-SiC MOSFET have been proposed as a possible way to reduce short channel effects such as DIBL, hot electron effects, and high electric fields. The gate of the DMG (Dual Material Gate) 4H-SiC MOSFET consists of two laterally contacting metals with different work functions in such a way that the threshold voltage near the source is more positive than that near the drain and thus the charge carrier more rapidly move in the channel. Lower work function gate at the drain side causes screening the drain voltage, which suppresses short-channel effects. Moreover, it is shown that dual material transistor has higher breakdown voltage.

Keywords: 4H-SiC, SCEs, DMG, SMG.

#### I. INTRODUCTION

4H-Silicon Carbide is a semiconductor with higher band gap than Silicon which makes it attractive for electronic devices in the fields of high temperature, high frequency and high power applications. The wide bandgap of 4H-SiC makes it suitable for operation in high temperature environments and leads to extremely low leakage currents for sensitive applications. Also the high thermal conductivity of 4H-SiC and ten times higher breakdown field than Silicon makes it suitable for high voltage and high current applications. In addition 4H-SiC has a natural oxide in the form SiO<sub>2</sub> which facilitates the fabrication of MOSFETs with 4H-SiC [1].

Among various polytypes, 4H-SiC is considered the most promising for MOSFET development, primarily due to its high intrinsic carrier mobility. Table 1 compares 4H-SiC with silicon [1]. Over the past few decades transistors gate length is scaled down aiming at improving the performance, and increase the number of components per chip. But reducing the gate length causes short channel effects to appear. The main short channel effects are lack of pinch-off and saturation due to large drain conductance and large leakage current (a shift in threshold voltage, and therefore dependence on drain voltage, due to drain induced barrier lowering (DIBL), and hot carrier effects) [2-3].

A MOSFET device is considered to be short when the channel length is the same order of magnitude as the depletion-layer widths of the source and drain junction. Several methods have been proposed to eliminate short channel effects [4-5] but none of them did not improve effective electron transport efficiency. Electron transport efficiency is related to the electric field distribution along the channel. Electrons enter into the channel with a low initial velocity and gradually accelerate in the direction of the channel. The greatest electron drift velocity is reached near the drain [6]. Consequently, the speed of the device is affected by a relatively slow electron drift velocity in the channel near the source area [7].

In 1999 Wei Long proposed a simple way to eliminate short channel effects and improve electron transport efficiency. He used two different materials as the gate metal, with different work functions such that the gate near the source had greater work function than the gate near the drain, contacting laterally to obtain a new device structure, dual material gate (DMG) FET. Therefore threshold voltage near the source was more positive than threshold voltage near the drain, and this improved carrier transport efficiency in the channel. More importantly, a step function in channel potential occurred which is the fundamental reason to reduce short-channel effects without sacrificing other device behaviors [7]. We use this idea for 4H-SiC MOSFET to reduce SCEs (short channel effects) and increase average electron velocity through the channel.

Table 1. Important physical properties of Silicon and polytype of SiC

|                                      | Silicon | 4H-SiC |

|--------------------------------------|---------|--------|

| Band gap (eV)                        | 1.1     | 3.26   |

| Intrinsic Electron Mobility (cm2/Vs) | 1400    | 1070   |

| Saturation Velocity (×107 cm/s)      | 1       | 2      |

| Critical Breakdown Field (MV/cm)     | 0.3     | 3      |

| Thermal Conductivity (W/K·cm)        | 1.5     | 4.9    |

# II. THE PROPOSED DMG STRUCTURE

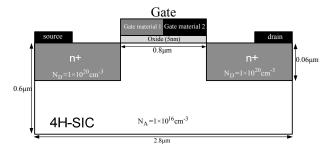

The cross section of the proposed structure is shown in Figure 1. Also the dimensions and doping levels are indicated. We must select two metals for the gate contact with different work functions. The work functions of gate

# 8th International Conference on "Technical and Physical Problems of Power Engineering" (ICTPE-2012) Fredrikstad, Norway, 5-7 September 2012

material1 (gold) and gate material2 (Chromium) are assumed 5.13 ev and 4.5 ev respectively. Hence there exist a 0.63 ev difference between the gate metals.

Figure 1. Dual material gate 4H-SiC MOSFET

# III. SIMULATION RESULTS

To investigate the proposed DMG structure, we simulate DMG 4H-SiC MOSFET and SMG (Single Material Gate) 4H-SiC MOSFET counterpart with the same physical and structural parameters, except for the single material gate structure.

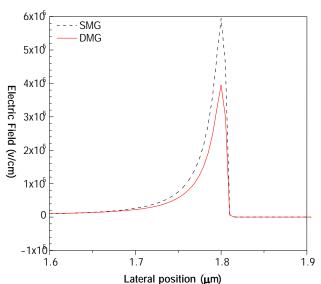

#### A. Electric Field

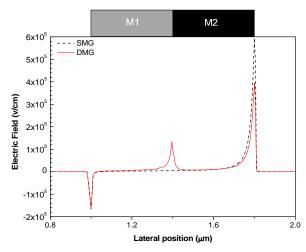

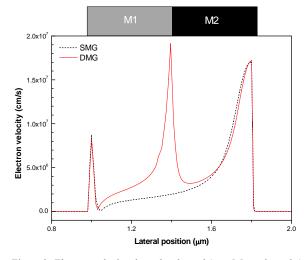

The simulated longitudinal electric field distribution of the DMG and SMG 4H-SiC MOSFETs are shown in Figure 2. Due to discontinuity of metal work function in DMG structure and according to the simulations, DMG structure shows two peaks in the electric field but the conventional SMG 4H-SiC MOSFET has only one peak near the drain. According to the relationship between electric field and electron velocity we expect an increase in the electron velocity along the channel of DMG structure compared to the conventional SMG device. Figure 3, shows the electron velocity along the channel of DMG and SMG structures. It is seen that electrons accelerate within the channel under gate 1, and reach a high peak velocity near the interface between the two gates, and travel a part of the channel with higher speed than the SMG structure, due to higher electric field in this region. This implies an increased average electron velocity along the channel. Moreover, due to the increase of the electric field at the interface of the two metals in DMG structure, the peak electric field at drain end is considerably reduced, resulting in reduced hot carrier effects.

#### **B. Screening and Suppression of Short-Channel Effects**

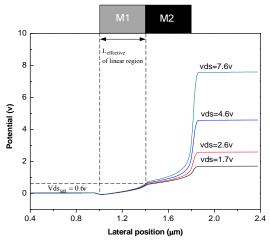

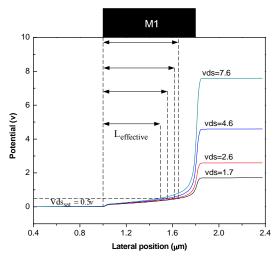

The important role of the DMG structure is suppressing short-channel effects due to the screening effect, which is induced by a step change of the potential along the channel. Figures 4 and 5 show the variations of the channel potential for different drain biases of DMG and SMG structures, respectively. The threshold voltage of DMG and SMG structures are 5.4 V and 5.5 V, respectively. For the SMG MOSFET, as the channel length is reduced, its departure from long-channel behavior is manifested by the drain current increasing with the drain bias. This departure, one of the short channel effects, arises as the result of channel length modulation due to the drain bias.

We expect that for the SMG 4H-SiC MOSFET with smaller length, the shift of the depleted region width after pinch off is comparable to the conventional SMG 4H-SiC MOSFET with longer channel length. But for the DMG 4H-SiC MOSFET , the effect of drain bias on the channel, i.e. channel length modulation, is effectively eliminated, because the channel under the first gate is screened from the drain bias after saturation and leading to decreased drain conductance.

It can be seen that, due to discontinuity of metal work function in DMG structure, after current saturation, the rise in potential occurs at the interface of the two metals and thus the additional drain voltage increase is not absorbed under the first gate (with larger work function), instead is absorbed under the second gate (with smaller work function). In the other words, the region under first gate is screened from the drain voltage variations and the effective channel length [7] is less sensitive to the drain voltage. As a result, the drain voltage has a very small influence on the drain current after saturation and therefore the drain conductance of DMG structure is reduced. This, results in reduced drain induced barrier lowering and increased output resistance of the DMG 4H-SiC MOSFET.

Figure 2. Electric field along the channel ( $V_{gs}$ =5.5v and  $V_{ds}$ =2v)

Figure 3. Electron velocity along the channel ( $V_{gs}$ =5.5v and  $V_{ds}$ =2v)

# 8th International Conference on "Technical and Physical Problems of Power Engineering" (ICTPE-2012) Fredrikstad, Norway, 5-7 September 2012

Figure 4. Channel potential profiles of DMG 4H-SiC-MOSFET for various drain biases. Screening effect is clearly seen ( $V_{gs}$ =6v)

Figure 5. Channel potential profiles of SMG 4H-SiC-MOSFET for various drain biases ( $V_{gs}$ =6v)

# C. Drain Induced Barrier Lowering (DIBL)

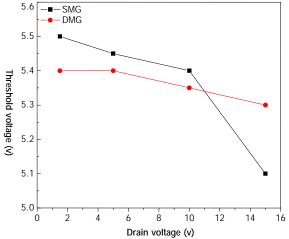

In devices with long channel lengths, the gate contact completely depletes the channel. When the gate length is reduced, a part of the depletion region is accomplished by the drain and source biases. In a short channel MOSFET the depletion region from the drain contact can reach the source side and reduce the barrier for electrons injecting from the source which allows electron flow between the source and the drain, even if the gate-source voltage is lower than the threshold voltage. As a result, the threshold condition can be reached at a lower gate voltage, since the drain voltage has already created a large depletion region. Threshold voltage variations due to the drain voltage for DMG and SMG structures are shown in Figure 6. According to simulation results, DMG structure shows better DIBL. The DIBL is found to reduce to 7.4 mV/V for DMG 4H-SiC MOSFET, in comparison to 30 mV/V of SMG 4H-SiC MOSFET. DIBL value can be calculated from equation (1):

$$DIBL = \frac{\Delta V_{th}}{\Delta V_d} \tag{1}$$

Figure 6. DIBL for DMG and SMG structures

#### **D. Hot Electron Effect**

The hot electron effect is described in as occurring when a high voltage is applied across the source and drain of a device, the electric field is high, and the electrons are accelerated in the channel. When the maximum field is increased further, carrier multiplication near the drain occurs, leading to substrate current and parasitic bipolar transistor action. High fields also cause hot carrier injection into the gate region, leading to threshold voltage shift and transconductance degradation [8]. The problem of hot electron has been increased as technologies scale down due to the fact that device features have scaled proportionally faster than voltage. Due to decrease in the electric near the drain in DMG structure as shown in Figure 7, dual material gate plays an important role in the reduction of the hot electron effect in the device.

Figure 7. Electric field near the drain for DMG and SMG structures  $(V_{gs}=5.5 \text{ and } V_d=2)$

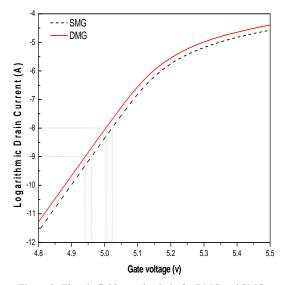

# E. Sub Threshold Swing

Subthreshold swing (SS) is defined as the gate voltage (Vgs) needed to increase the drain current one order of magnitude in subthreshold regime and can be calculated from Equation (2):

$$SS = \ln 10 \frac{dV_{gs}}{d(\ln I_{ds})} \tag{2}$$

SS is an important parameter in very short-channel lengths transistors [9]. A small subthreshold swing is highly desired since it improves the ratio between the on and off-currents. The subthreshold characteristics for DMG and SMG structures are shown in Figure 8. Both devices show excellent subthreshold swing of only 62 milivolt per decade.

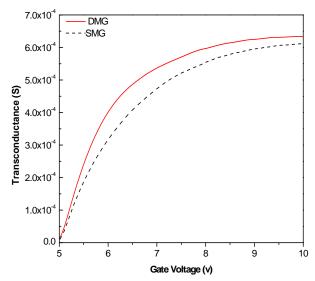

#### F. The Transconductance

The DMG 4H-SiC MOSFET has higher transconductance as shown in Figure 9. Up to 20% improvement is observed for the DMG 4H-SiC-MOSFET. In this case drain to source voltage  $V_{ds}$ =10 V, which places devices in saturation mode of operation.

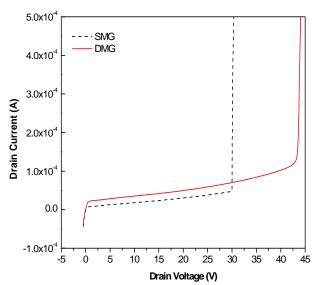

# G. Breakdown Voltage

In this section the effect of the DMG structure on the breakdown voltage of the transistor is analyzed. For the DMG 4H-SiC MOSFET, due to decrease in electric field near the drain, we expect a higher breakdown voltage than the SMG structure. Typical I-V characteristics of 4H-SiC DMG and SMG-MOSFETs are shown in Figure 10. Nearly to 44% improvement of the breakdown voltage is observed for the DMG 4H-SiC MOSFET in comparison to SMG 4H-SiC MOSFET. The breakdown voltage is found to be increased to 44 V for DMG 4H-SiC MOSFET compared to 30 V of the SMG 4H-SiC MOSFET.

Figure 8. Electric field near the drain for DMG and SMG structures  $(V_{gs}$ =5.5 and  $V_d$ =2)

# IV. CONCLUSIONS

In this work, the effectiveness of the dual material gate concept to the 4H-SiC MOSFET has been examined for the first time by using a two-dimensional simulation study. Shortchannel effects are investigated in this study. Our results show that the dual material gate structure is a good choice for eliminating short channel effects such as hot electron effect and DIBL in 4H-SiC MOSFET.

Moreover, carrier transport efficiency and breakdown voltage improves due to a more uniform electric field along the channel. Also both drive current and transconductance of DMG-4H-SiC MOSFET's significantly exceed that of conventional ones owing to the velocity enhancement.

Figure 9. Transconductance as a function of gate voltage for DMG and SMG structures

Figure 10. I-V<sub>DS</sub> characteristics for DMG and SMG structures  $(V_{gs}$ =5.5v)

#### REFERENCES

[1] S. Potbhare, "Modeling and Characterization of 4H-Silicon Carbide MOSFETs: High Field, High Temperature, and Transient Effects", Ph.D. Dissertation, College Park, University of Maryland, 2008.

[2] Y. Awano, M. Kosugi, K. Kosemura, T. Mimura, M. Abe, "Short-Channel Effects in Subquarter-Micrometer-Gate HEMTs: Simulation and Experiment", IEEE Transactions on Electron Devices, Vol. 36, pp. 2260-2266, 1989.

[3] U.K. Mishra, A.S. Brown, S.E. Rosenbaum, "DC and RF Performance of 0.1-mm Gate Length Al<sub>0.48</sub>As/Ga<sub>0.47</sub>In<sub>0.53</sub>As Pseudomorphic HEMT", Electron

# 8th International Conference on "Technical and Physical Problems of Power Engineering" (ICTPE-2012) Fredrikstad, Norway, 5-7 September 2012

Devices Meeting, IEDM '88, International Technical Digest., pp. 180-183, 1988..

- [4] T. Furutsuka, M. Ogawa, N. Kawamura, "GaAs Dual-Gate MESFET's", IEEE Transactions on Electron Devices, Vol. 25, pp. 580-586, 1978.

- [5] L.D. Nguyen, A.S. Brown, M.A. Thompson, L.M. Jelloian, "50-nm Self-Aligned-Gate Pseudomorphic AlInAs/GaInAs High Electron Mobility Transistors", IEEE Transactions on Electron Devices, Vol. 39, pp. 2007-2014, 1992.

- [6] A. Cappy, B. Carnez, R. Fauquembergues, G. Salmer, E. Constant, "Comparative Potential Performance of Si, GaAs, GaInAs, InAs Submicrometer-Gate FET's", IEEE Transactions on Electron Devices, Vol. 27, pp. 2158-2160, 1980.

- [7] W. Long, H. Ou, J.M. Kuo, K.K. Chin, "Dual-Material Gate (DMG) Field Effect Transistor", IEEE Transactions on Electron Devices, Vol. 46, pp. 865-870, 1999.

- [8] W. Long, "Dual Material Gate Field Effect Transistor (DMG-FET)", Ph.D. Dissertation, Institute of Technology, New Jersey, 1997.

- [9] M.M. Mattausch, H.J. Mattausch, T. Ezaki, "The Physics and Modeling of MOSFETS: Surface-Potential Model HiSIM", Japan: World Scientific, 2008.

#### **BIOGRAPHIES**

Mohammadali Moradian was born in Yasuj, Iran, 1985. He received the B.Sc. degree from Sadjad University of Mashhad (Mashhad, Iran) in Electrical Engineering, in 2007. He is currently working toward the M.Sc. degree in Electrical Engineering at University of Sabzevar (Sabzevar,

Iran). His research interests include modeling and simulation of novel devices structures on 4H-SiC and silicon-on-insulator (SOI) MOSFETs.

**Seyed Ebrahim Hosseini** received the B.Sc. degree in Electrical Engineering from Isfahan University of Technology, Isfahan, M.Sc. from Tarbiat Modarres University, Tehran, Iran, and Ph.D. degree in Electrical Engineering from Sharif University of Technology, Tehran, Iran, in 2001.

He is now Associate Professor of Electronics Engineering at Ferdowsi University of Mashhad, Mashhad, Iran. His research areas include microelectronic devices, SOI transistors, and device modeling and simulation. He has authored or co-authored over 70 conference and journal papers.