### Contents lists available at SciVerse ScienceDirect

## Physica E

journal homepage: www.elsevier.com/locate/physe

CrossMark

# A novel AlGaN/GaN HEMT with a p-layer in the barrier

S.M. Razavi <sup>a,\*</sup>, S.H. Zahiri <sup>a</sup>, S.E. Hosseini <sup>b</sup>

- <sup>a</sup> Faculty of Engineering, University of Birjand, Birjand, Iran

- <sup>b</sup> Faculty of Engineering, Ferdowsi University of Mashhad, Mashhad, Iran

- Simulation results disclose that compared to the conventional and T-gate structures the structure with p-layer in the barrier (PL-HEMT) optimizes the breakdown voltage.

- It reduces the gate–drain capacitance ( $C_{\rm gd}$ ).

- It decreases the output conductance (g<sub>o</sub>).

- It reduces the short channel effect.

## ARTICLE INFO

#### Article history: Received 25 December 2012 Received in revised form 6 May 2013 Accepted 17 May 2013 Available online 3 June 2013

Keywords:

GaN HEMT

Short channel effect

Gate capacitance

Electric field

DC output conductance

Sub-threshold slope

#### ABSTRACT

The potential impact of gallium-nitride (GaN) high electron mobility transistor (HEMT) with a p-layer in the barrier is reported. We investigate the device performance focusing on short channel effects, gatedrain capacitance, electric field, breakdown voltage, DC output conductance ( $g_o$ ), drain current, DC transconductance ( $g_m$ ) and sub-threshold slope using two-dimensional and two-carrier device simulations. Our simulation results reveal that the proposed structure reduces the short channel effects, gate–drain capacitance, sub-threshold slope and  $g_o$  compared to the conventional and T-gate structures. Also this new structure reduces the peak electric field at the gate corner near the drain and consequently increases the breakdown voltage significantly. Increasing p-layer length ( $L_p$ ) and thickness ( $T_p$ ), improves the breakdown voltage, short channel effects, gate–drain capacitance and  $g_o$ .

© 2013 Elsevier B.V. All rights reserved.

#### 1. Introduction

In recent decades, due to unique characteristics such as a wide band-gap, superior carrier saturation velocity, a large breakdown field strength and strong spontaneous and piezoelectric polarization, GaN-based high-electron mobility transistors (HEMTs) have attracted considerable attentions and shown excellent performance in high-power and high-frequency electronic applications [1,2]. With their excellent performances in high-power operations at microwave frequencies, wide-band gap AlGaN/GaN HEMTs are emerging as the promising candidates for next generation RF/microwave power amplifiers [3].

In this paper, the potential impact of AlGaN/GaN HEMT with a p-layer in the barrier is studied using a two-dimensional (2-D) device simulator. The unique features of the AlGaN/GaN HEMT with a p-layer in the barrier (PL-HEMT) are explored and compared with those of T-gate [4] and conventional [1] HEMTs in terms of short channel effects, gate-drain capacitance, electric

field, breakdown voltage, DC output conductance  $(g_o)$ , DC transconductance  $(g_m)$ , sub-threshold slope and drain current. In the next section, the proposed structure dimensions and the physical models used in the 2-D simulation are described in detail. In the third section, we first explain how the presence of the p-layer in the barrier will increase breakdown voltage. Also, in this section, the effect of p-layer length and thickness on the short channel effect, gate—drain capacitance, output conductance, drain current and  $g_m$  are studied and compared with those in T-gate and conventional structures in details. After that, the sub-threshold slopes of the PL-HEMT as a function of gate length are plotted and compared to those of the conventional and T-gate structures.

## 2. Device structure

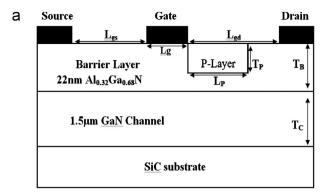

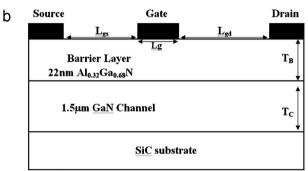

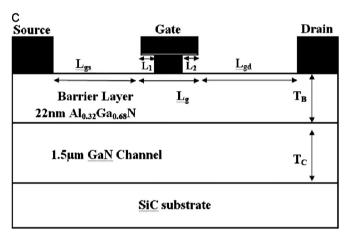

Fig. 1(a), (b) and (c) shows the schematic cross-section of PL-HEMT, conventional [1] and T-gate [4] structures, respectively. The dimensions of the PL-HEMT, T-gate and conventional structures are as follows: gate length  $L_{\rm g}{=}0.5~\mu{\rm m}$ , gate–drain spacing  $L_{\rm gd}{=}1~\mu{\rm m}$ , gate–source spacing  $L_{\rm gs}{=}1~\mu{\rm m}$ . Barrier layer and channel

<sup>\*</sup>Corresponding author. Tel./fax: +98 571 4411160.

E-mail address: m.136287@gmail.com (S.M. Razavi).

Fig. 1. Cross section of the (a) PL-HEMT, (b) conventional and (c) T-gate structures.

thicknesses are  $T_{\rm B}{=}22$  nm and  $T_{\rm C}{=}1.5~\mu{\rm m}$ , respectively. The barrier layer is a n-type heavily doped  ${\rm Al_{0.32}Ga_{0.68}N}$  while the channel layer is an intrinsic GaN. Also, the p-layer in the barrier is a p-type heavily doped  ${\rm Al_{0.32}Ga_{0.68}N}$ . The doping concentration of the barrier layer is the same as that of the p-layer.  $L_1$  and  $L_2$  in the T-gate structure have the same lengths of 0.1  $\mu{\rm m}$ . Nickel is chosen for the gate Schottky contact with a work function of 5.1 eV. It is worth noting that the PL-HEMT and conventional structures can be fabricated using the same procedure as reported in Ref. [1]. The devices are simulated using two-dimensional ATLAS software [5]. In order to achieve more realistic results, several models are activated in simulations, including the 'SRH' model for Shockley–Read–Hall recombination, the 'Conmob' model for standard concentration dependent mobility, the 'Fldmob' model for parallel electric field-dependent mobility and the 'Fermi Dirac' model for statistics [6,7].

#### 3. Results and discussion

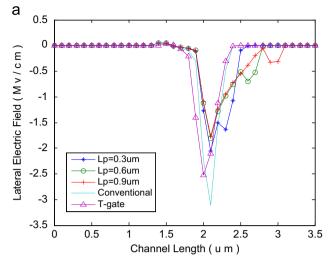

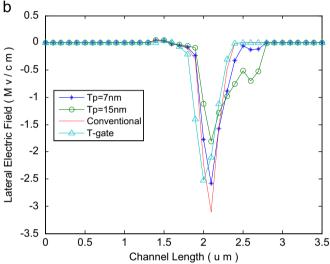

Fig. 2(a) and (b) shows the lateral electric field at the gate corner near the drain at  $V_{\rm DS}=80\,{\rm V}$  and  $V_{\rm GS}=-4\,{\rm V}$  for different

$L_{\rm P}$  and  $T_{\rm P}$ , respectively. It is obvious from these figures that increasing  $L_P$  and  $T_P$  in the PL-HEMT reduces the maximum lateral electric field at the gate corner near the drain compared to the conventional and T-gate structures. A further investigation shows that the breakdown happened at gate corner near the drain due to the electric field crowding [8,9]. Hence, it can be deduced that the PL-HEMT with different  $L_P$  and  $T_P$  have a larger breakdown voltages than those of the conventional and T-gate structures. Also, as can be shown in these two figures, increasing  $L_P$  and  $T_P$  reduces the maximum electric field and consequently increases the breakdown voltage. In this work, the critical electric field of the GaN (3.5 MV/cm) is used to determine the breakdown voltage. Increasing the drainsource voltage increases the electric field in the channel. The breakdown voltage is nominated the drain-source voltage that maximum electric field in the channel is equal to the critical electric field. It is clear from the simulation results that the breakdown voltage for the PL-HEMT structure with  $L_P$ =0.3  $\mu$ m, 0.6  $\mu$ m and 0.9  $\mu$ m at a fixed  $T_P$ (15 nm) are about 200 V, 250 V and 270 V, respectively. The breakdown voltage for the PL-HEMT structure with  $T_P = 7$  nm and 15 nm at a fixed  $L_P$  (0.6  $\mu$ m) are about 150 V and 220 V, respectively. Also, the breakdown voltage in the conventional and T-gate structures are about 90 V and 150 V, respectively. Because of Field plate in the drain side, the T-gate structure has larger breakdown voltage than that of the conventional structure. The maximum breakdown voltage is obtained in the PL-HEMT with  $L_P$ =0.9  $\mu$ m and  $T_P$ =15 nm. Therefore, the breakdown voltage of PL-HEMT (~270 V) is significantly improved compared to that of the conventional (~90 V) and T-gate (~150 V) structures.

The device performance can be greatly improved by reducing the gate length to enhance the trans-conductance and reduce the gate capacitance. On the other hand as the technology is pushing the gate length to the sub-quarter micrometer range, short channel effects are becoming increasingly significant. One of the most pervasive short channel effects is the drain-induced barrier lowering (DIBL). DIBL is an electrostatic effect causing the barrier between the source and the drain of a field effect transistor (FET) in or near the sub-threshold region to be lowered when the drain voltage is increased. This effect causes the channel to return from a pinch-off state to conduct and shifts the threshold voltage. Consequently, the DIBL places a hard limit on the minimum gate size and degrades the trans-conductance and output conductance, which are critical to the gain and power output for a power FET and the noise margin for a digital FET [10–12].

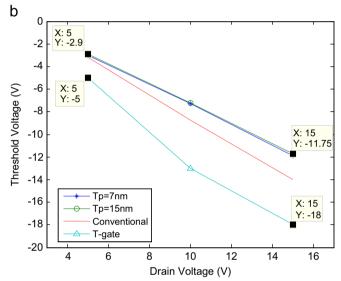

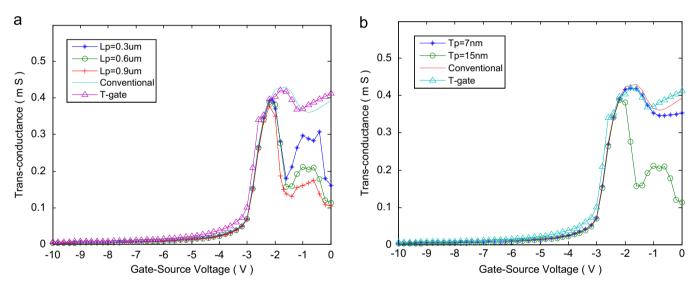

Fig. 3(a) reveals that the negative shift in the threshold voltage with increase in the drain voltage for different  $L_P$  at a fixed  $T_P$ (15 nm) in the PL-HEMT structure is less than that in the conventional and T-gate structures. As is evident from this figure, a larger L<sub>P</sub> can be used to reduce the negative shift in the threshold voltage with increase in the drain voltage. Therefore, increasing  $L_p$  reduces the short channel effect such as DIBL. For example, according to this figure, the negative shift values in the threshold voltage with increase in the drain voltage of PL-HEMT ( $T_P=15 \text{ nm}$  and  $L_{\rm p}$ =0.9  $\mu$ m), conventional and T-gate structures are -8.75 V, -10.5 V and -13 V, respectively. This is because a larger  $L_{\rm P}$ decreases the maximum lateral electric field in Fig. 2(a) and then reduces dependence of the threshold voltage to the drain voltage. As can be shown in Fig. 3(b), increasing  $T_P$  at a fixed  $L_P$  (0.6  $\mu$ m) for PL-HEMT reduces the negative shift in the threshold voltage. For instance, it is evident from this figure that the negative shift in the threshold voltage with increase in the drain voltage at PL-HEMT  $(T_{\rm P}=15~{\rm nm}~{\rm and}~L_{\rm p}=0.6~{\rm \mu m})$ , conventional and T-gate structures are -8.5 V, -10.5 V and -13 V, respectively. It can be concluded from Fig. 3(a) and (b) that a larger  $L_p$  and  $T_P$  can be used to reduce the short channel effect such as DIBL.

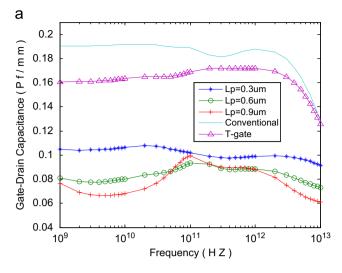

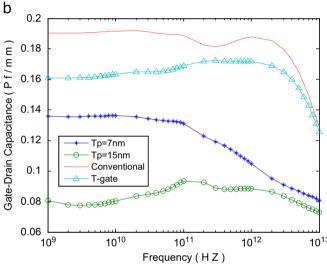

Gate-drain capacitance with respect to the frequency for different  $L_{\rm p}$  and  $T_{\rm P}$  in the PL-HEMT at  $V_{\rm GS}{=}0~{\rm V}$  and  $V_{\rm DS}{=}20~{\rm V}$

**Fig. 2.** Lateral electric field as a function of the channel length for different (a)  $L_{\rm p}$  at a fixed  $T_{\rm P}$  (15 nm) and (b)  $T_{\rm P}$  at a fixed  $L_{\rm p}$  (0.6  $\mu$ m) in the PL-HEMT, conventional and T-gate structures at  $V_{\rm CS}$ =-4 V and  $V_{\rm DS}$ =80 V.

conditions are plotted and compared with the conventional and T-gate structures in Fig. 4(a) and (b), respectively. It is obvious from these figures that gate-drain capacitance is decreased with increasing  $L_{\rm p}$  and  $T_{\rm P}$ . Also, for different  $L_{\rm p}$  and  $T_{\rm P}$ , gate–drain capacitance in the PL-HEMT is smaller than that in the conventional and T-gate structures. It is also clear in these two figures that the p-layer in the barrier decreases net electrons density in the channel, because the net donor impurities density in the barrier is reduced. This in turn decreases the gate-drain capacitance and consequently improves high frequency performance. As is displayed in these figures, the minimum gate-drain capacitance is obtained in the PL-HEMT with  $L_{\rm p}$ =0.9  $\mu m$  and  $T_{\rm P}$ =15 nm. It is worth noting that gate-drain capacitance reduction due to increasing  $L_{\rm p}$  is more significant than that due to increasing  $T_{\rm p}$ . It can be concluded that the PL-HEMT structure has lesser gate-drain capacitance than those in the conventional and T-gate structures. Therefore, the PL-HEMT has better high frequency performance compared to the conventional and T-gate structures.

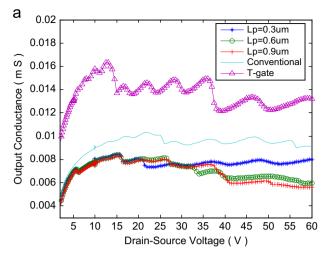

The output conductance  $(g_0)$  can be calculated by differentiating the drain current with respect to drain–source voltage at a constant gate–source voltage:

$$g_{o} = \frac{\partial I_{D}}{\partial V_{DS}} \Big|_{Vgs = const} \tag{1}$$

**Fig. 3.** Threshold voltage as a function of drain voltages for different (a)  $L_{\rm p}$  at a fixed  $T_{\rm P}$  (15 nm) and (b)  $T_{\rm P}$  at a fixed  $L_{\rm p}$  (0.6  $\mu$ m) in the PL-HEMT, conventional and T-gate structures.

$g_{\rm o}$  shows the drain current dependence to drain–source voltage at a fixed gate–source voltage. Fig. 5(a) and (b) shows the output conductance with respect to drain–source voltage at  $V_{\rm CS}=-4$  V for different  $L_{\rm p}$  and  $T_{\rm P}$  in PL-HEMT, conventional and T-gate structures, respectively. As is obvious from these figures, the output conductance in the PL-HEMT structure for different  $L_{\rm p}$  and  $T_{\rm P}$  is smaller than those of the conventional and T-gate structures. This is because the p-layer in the barrier reduces the lateral electric field compared to the conventional structure, as it was displayed in Fig. 2(a) and (b). This reduces the drain–source voltage control on the channel and therefore reduces  $g_{\rm o}$ . Comparing Fig. 5(a) and (b) illustrates that increasing  $L_{\rm p}$  and  $T_{\rm P}$  reduces  $g_{\rm o}$ . However, increasing  $L_{\rm p}$  has bigger effect in the  $g_{\rm o}$  in comparison with increasing  $T_{\rm p}$ . The minimum  $T_{\rm p}=15$  nm.

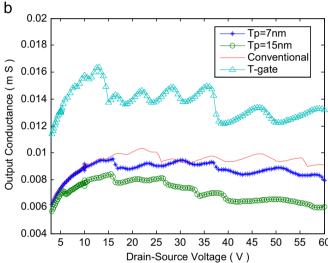

Drain currents with respect to the drain–source voltages at  $V_{\rm GS}$ =-1 V in PL-HEMT with different  $L_{\rm P}$  and  $T_{\rm P}$  are plotted and compared with conventional and T-gate structures in Fig. 6(a) and (b). According to these figures, decreasing  $L_{\rm P}$  and  $T_{\rm P}$  increases the drain current. It is obvious that inserting a p-layer in the barrier of HEMT decreases net electrons density in the channel, because the net donor impurities density in the barrier is reduced. This causes

**Fig. 4.** Gate–drain capacitance as a function of the frequency for different (a)  $L_{\rm p}$  at a fixed  $T_{\rm P}$  (15 nm) and (b)  $T_{\rm P}$  at a fixed  $L_{\rm p}$  (0.6  $\mu$ m) in the PL-HEMT, conventional and T-gate structures at  $V_{\rm GS}$ =0 V and  $V_{\rm DS}$ =20 V.

a small reduction in the drain current compared to the conventional structure. As Fig. 6 shows, this reduction is small and compared to improvement in the breakdown voltage, DIBL, gatedrain capacitance and  $g_{\rm o}$ , the overall device performance is improved considerably. However, it is worth noting that the T-gate structure has bigger drain current than that in the PL-HEMT and conventional structures.

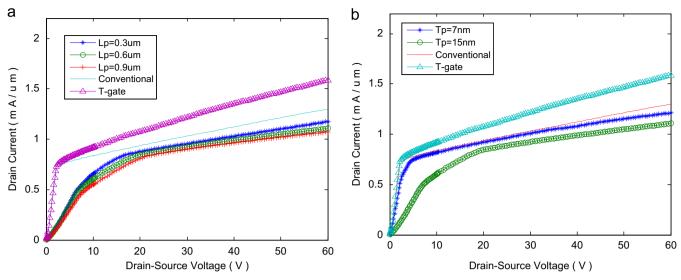

The trans-conductance  $(g_m)$  can be calculated by differentiating the drain current with respect to gate–source voltage at a constant drain–source voltage:

$$g_{\rm m} = \frac{\partial I_{\rm D}}{\partial V_{\rm GS}} \Big|_{Vds = const}$$

(2)

$G_{\rm m}$  shows the drain current dependence to gate–source voltage at a fixed drain–source voltage. Fig. 7(a) and (b) shows the transconductance with respect to gate–source voltage at  $V_{\rm DS}=10~{\rm V}$  for different  $L_{\rm P}$  and  $T_{\rm P}$  in PL-HEMT, conventional and T-gate structures, respectively. As is evident from these figures,  $g_{\rm m}$  in the T-gate structure is larger than that in the PL-HEMT structure. Because, the connected gate length to the channel in this structure is less than that in the PL-HEMT structure. The  $g_{\rm m}$  value in the conventional structure is almost equal to that in the T-gate structure. Also,

**Fig. 5.** Output conductance as a function of drain voltages for different (a)  $L_{\rm p}$  at a fixed  $T_{\rm P}$  (15 nm) and (b)  $T_{\rm P}$  at a fixed  $L_{\rm p}$  (0.6  $\mu$ m) in the PL-HEMT, conventional and T-gate structures at  $V_{\rm GS}$ = -4 V.

$L_{\rm p}$  and  $T_{\rm P}$  reduction in the PL-HEMT structure can be used to increase the  $g_{\rm m}$ .

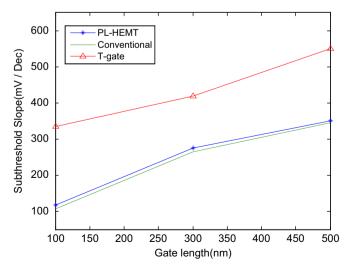

Fig. 8 compares the sub-threshold slope of our proposed structure to those of conventional and T-gate structures as a function of gate length. In our devices, the sub-threshold slope is extracted at a  $V_{\rm DS}$  of 1 V. Both PL-HEMT and conventional structures exhibit almost equivalent sub-threshold slopes. But, the sub-threshold slope in the T-gate structure is bigger than those in the conventional and PL-HEMT structures. Gate length variation causes a significant change in the sub-threshold slope. Decreasing gate length improves the sub-threshold slope of conventional, PL-HEMT and T-gate structures. It can be easily seen that the proposed structure has better sub-threshold characteristics than that of T-gate structure for all gate lengths.

#### 4. Conclusion

To improve the breakdown voltage, short channel effects, gatedrain capacitance, sub-threshold slope and the output conductance, we have proposed a novel device structure called the PL-HEMT that has a p-layer in the barrier. This new structure reduces maximum lateral electric field in the channel and consequently

Fig. 6. Drain currents as a function of drain voltages for different (a)  $L_p$  at a fixed  $T_P$  (15 nm) and (b)  $T_P$  at a fixed  $L_p$  (0.6  $\mu$ m) in the PL-HEMT, conventional and T-gate structures at  $V_{CS} = -1$  V.

Fig. 7. DC Trans-conductance as a function of gate–source voltages for different (a)  $L_p$  at a fixed  $T_P$  (15 nm) and (b)  $T_P$  at a fixed  $L_p$  (0.6  $\mu$ m) in the PL-HEMT, conventional and T-gate structures at  $V_{DS}$  = 10 V.

**Fig. 8.** Sub-threshold slope as a function of gate length in the PL-HEMT ( $L_p$ =0.9  $\mu$ m,  $T_p$ =15 nm), conventional and T-gate structures at  $V_{DS}$ =1 V.

improves the breakdown voltage. The breakdown voltage of 270 V is obtained for the PL-HEMT compared with 90 V of the conventional and 150 V of T-gate in expense of slightly reduction in the drain current. Our simulation results show that the proposed structure has smaller gate—drain capacitance and  $g_{\rm o}$  in comparison with the conventional and T-gate structures. Also, maximum lateral electric field reduction in the PL-HEMT reduces short channel effects such as DIBL.

## References

- [1] M. Juncai, Z. Jincheng, X. Junshuai, L. Zhiyu, L. Ziyang, X. Xiaoyong, M. Xiaohua, H. Yue, Journal of Semiconductors 33 (1) (2012) 14002.

- [2] W. Chong, H. Yunlong, Z. Xuefeng, H. Yue, M. Xiaohua, Z. Jincheng, Journal of Semiconductors 33 (3) (2012) 34003.

- [3] J. Liu, Y. Zhou, J. Zhu, Y. Cai, K.M. Lau, K.J. Chen, IEEE Transactions on Electron Devices 54 (1) (2007) 2.

- [4] R. Gupta, S. Rathi, M. Gupta, R.S. Gupta, Superlattices and Microstructures 47 (2010) 779.

- [5] ATLAS user's manual: Device simulation software, Silvaco International, September 2005.

- [6] S.E.J. Mahabadi, A.A. Orouji, P. Keshavarzi, H.A. Moghadam, Semiconductor

- Science and Technology 26 (2011) 95005.

[7] A.A. Orouji, S.M. Razavi, S.E. Hosseini, H.A. Moghadam, Semiconductor Science and Technology 26 (2011) 115001.

- [8] C.L. Zhu, C.C. Rusli, G.H. Tin, S.F. Zhang, J. Yoon, Microelectronic Engineering 83 (2006) 92.

- [9] J. Zhang, X. Luo, Z. Li, B. Zhang, Microelectronic Engineering 84 (2007) 2888.

- [10] S.M. Razavi, A.A. Orouji, S.E. Hosseini, Materials Science in Semiconductor Processing 15 (2012) 516.

- [11] C.S. Chang, D.Y.S. Day, S. Chan, IEEE Transactions on Electron Devices 37 (5) (1990) 1182.

- [12] P. Pandey, B.B. Pal, S. Jit, Electron Devices 51 (2) (2004) 246.