## International Journal of Engineering

Journal Homepage: www.ije.ir

## Accurate Analytical Modeling of Drain Current of Heterojunction Tunneling Field Effect Transistor

F. Peyravi, S. E. Hosseini\*

Department of Electrical Engineering, Ferdowsi University of Mashhad, Iran

### PAPER INFO

Paper history:

Received 10 October 2023

Received in revised form 13 December 2023

Accepted 31 December 2023

Keywords: Analytical Model Heterojunction Tunneling Field Effect Transistor Band-to-band Tunneling Tangent Line Approximation

### ABSTRACT

An accurate analytical model is presented for drain current of the heterojunction tunneling field effect transistor, taking into account the source depletion region, mobile charges and the effect of the drain voltage. This model accurately predicts the potential distribution not only on the surface but also within the semiconductor depth by utilizing newly formulated mathematical relationships. Using the tangent line approximation method and considering the channel region as well as the source depletion region' We analytically calculate the band-to-band tunneling current from the source to the channel by integrating the tunneling generation rate. Compared to simulation results, the proposed model demonstrates significant accuracy in predicting drain current.

doi: 10.5829/ije.2024.37.07a.12

## 1. INTRODUCTION

In recent years, the Tunneling Field-Effect Transistor (TFET) has garnered significant attention due to its

ability to achieve a sub-threshold swing of less than 60 mV/dec, which is a fundamental limitation in Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs). This characteristic positions TFET as a

Please cite this article as: Peyravi F, Hosseini SE. Accurate Analytical Modeling of Drain Current of Heterojunction Tunneling Field Effect Transistor. International Journal of Engineering, Transactions A: Basics. 2024;37(07):1331-42.

<sup>\*</sup>Corresponding Author Email: <a href="mailto:ehosseini@um.ac.ir">ehosseini@um.ac.ir</a> (S. E. Hosseini)

promising alternative to MOSFETs in low-power applications and future electronic devices technology. Additionally, TFET demonstrates low leakage current and increased immunity against short-channel effects (SCEs) (1-4).

To facilitate circuit design utilizing TFETs, the development of an accurate analytical model for the drain current is of paramount importance (5). A robust analytical model should rely on physical phenomena, enabling the expression of device characteristics through mathematical equations. Numerous numerical and analytical models have been proposed for TFETs in the existing literature (6, 7). While numerical and semianalytical models offer reasonably accurate results; their efficiency in circuit-level simulations is limited. Conversely, analytical models are compatible with a wide range of circuit-level simulation tools, making them more practical for this purpose. Analytical models for TFETs generally rely on surface potential computation. However, some models have previously utilized the average electric field across the tunneling junction to calculate the tunneling generation rate. This approach, unfortunately, has limited the accuracy of the model (8, 9). To address this limitation, it is recommended to consider the complete electric field profile along the tunneling junction. By incorporating the full electric field profile, the model accuracy can be significantly improved.

Tangent line method is adopted for drain current calculation to consider total generation profile (10-12). While these models take into account the electric field profile across the tunneling junction to enhance the accuracy of the model, they primarily focus on the electric field along the channel depletion region and overlook the depletion region in the source region.

Furthermore, in order to calculate the generation rate, the electric field at the semiconductor surface is determined, assuming that the electric field throughout the depth of the semiconductor layer remains constant and equal to the surface electric field. However, in reality, this assumption is rarely valid in actual devices (13). Artificial intelligence can be useful in optimizing analytical models and the control of various systems as a powerful tool at the global level (14).

In this paper, we proposed an accurate twodimensional (2D) solution to Poisson equation in the channel of the TFET.

In addition to the surface potential, we considered the potential distribution in the semiconductor depth, and thefore, we were able to calculate the potential more accurately than reported literature, by utilizing newly formulated mathematical relationships.

This solution provides an accurate prediction of the electric field not only at the surface but also throughout the depth of the semiconductor layer. Finally, we developed an analytical model for drain current using the tangent line approximation method, which considers the

source depletion region. Comparing with simulation results are shown that the proposed model has impressive accuracy.

This paper is organized as follows: In section 2, the device structure under consideration is introduced. In section 3, an analytical surface potential model is proposed in detail. In section 4, an analytical model for drain current by applying the tangent line approximation method is expressed. The results of analytical model and comparison with simulation results are presented in section 5.

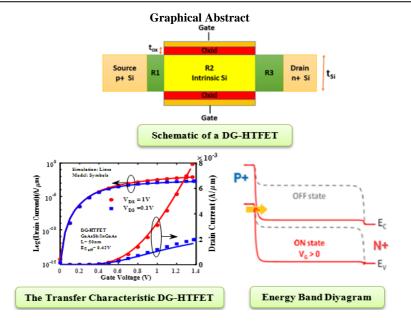

## 2. DEVICE STRUCTURE

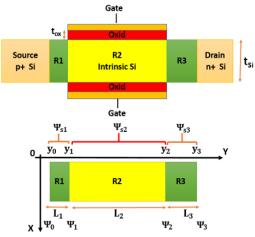

The schematic diagram of the H-TFET is depicted in Figure 1. In this device, two depletion regions are formed at the source-channel junction and the channel-drain junction. At a certain value of the gate voltage  $V_{GS}$ , the valence band in the source is aligned with the conduction band in the channel, and electrons can tunnel from the source valence band into the channel conduction band through the potential barrier formed by the bandgap. Device specifications are summarized in Table 1 (15-17).

## 3. ANALYTICAL MODEL DESCRIPTION

Analytical modeling of TFET typically involves three steps. The first step is calculating the surface potential of the transistor. The second step is determining the tunneling generation rate, and in the third step, integrating the tunneling rate to calculate drain current.

## **3. 1. Surface Potential and Electric Field Model** A pseudo-2D method together with the parabolic

**Figure 1.** schematic diagram of the proposed double gate heterojunction tunnel field effect transistor (DG-HTFET) considering the areas included (source depletion region R1, channel region R2, drain depletion region R3)

**TABLE 1.** Device parameters used in simulations and analytical model

| Physical parameters                                    | Value                                       |

|--------------------------------------------------------|---------------------------------------------|

| Gate length ( $L_G$ )                                  | 50 nm                                       |

| Source length $(L_S)$                                  | 30 nm                                       |

| Drain length $(L_D)$                                   | 30 nm                                       |

| Source doping (p-type)                                 | $10^{20}\mathrm{cm^{-3}}$                   |

| Drain doping (n-type)                                  | $5 \times 10^{18}  \text{cm}^{-3}$          |

| Channel doping                                         | $10^{17}\mathrm{cm^{-3}}$                   |

| Channel thickness $(t_{si})$                           | 10 nm                                       |

| Oxide thickness $(t_{ox})$                             | 2,3 nm                                      |

| Permittivity of Si $(\varepsilon_{Si})$                | $11.68 \ \varepsilon_0$                     |

| Permittivity of SiGe ( $\varepsilon_{SiGe}$ )          | $13.9 \ \varepsilon_0$                      |

| Permittivity of GaAsSb ( $\varepsilon_{GaAsSb}$ )      | $14.3 \ \varepsilon_0$                      |

| Permittivity of InGaAs ( $\varepsilon_{InGaAs}$ )      | $13.9 \ \varepsilon_0$                      |

| Permittivity of $SiO_2(\boldsymbol{\varepsilon_{ox}})$ | $3.9 \ \varepsilon_0$                       |

| Work function of gate material $(\emptyset_m)$         | 4.5,4.8 eV                                  |

| Kane's parameter ( $A_{BTBT}$ )                        | $3.5{\times}10^{21}~eV^{1/2}\!/cm.s.V^2$    |

| Kane's parameter ( $B_{BTBT}$ )                        | 22.5×10 <sup>6</sup> V/cm.eV <sup>3/2</sup> |

potential approximation for solving Poisson equation is used to obtain a 2D potential profile. The Poisson equation given below:

$$\frac{\partial^2 \Psi(x,y)}{\partial x^2} + \frac{\partial^2 \Psi(x,y)}{\partial y^2} = \frac{-qN_S}{\varepsilon_S} \tag{1}$$

In this equation,  $\Psi(x,y)$  is the electrostatic potential in the device, which is measured with respect to substrate Fermi level,  $\varepsilon_s$  is the semiconductor permittivity, q is electron charge, and  $N_s$  is effective doping density.  $N_s$  is equal to  $-N_1$  in p-type source, and is equal to  $N_2$  and  $N_3$  in n-type channel and drain regions, respectively. In Equation 1 mobile charges are ignored and its effect is considered in section B.

Pseudo 2-D method is adopted to convert the 2-D Poisson equation into an effective 1-D equation which is further used to obtain the potential distribution along the thickness of the device. Poisson equation is solved in three regions, i.e., the source depletion region (R1), the low doped channel (R2) and the drain depletion region (R3) using proper boundary conditions. Assuming parabolic solution for the Poisson equation, the 2-D potential distribution is written as (15, 18).

$$\Psi(x,y) = a_0(y) + a_1(y)x + a_2(y)x^2 \tag{2}$$

Coefficients  $a_0(y)$ ,  $a_1(y)$  and  $a_2(y)$  in Equation 2 are computed using boundary conditions, i.e., continuity of the potential and the electric displacement at the insulator-semiconductor interfaces. The potential distribution at the front-oxide-channel interface (x=0), and back-oxide-semiconductor interface ( $x=t_s$ ) are denoted as  $\Psi_s(y)$  and  $\Psi_b(y)$ , respectively.

$$\Psi(0,y) = \Psi_{S}(y) \tag{3a}$$

$$\Psi(t_s, y) = \Psi_h(y) \tag{3b}$$

The electric field displacement at front and back surfaces are continuous and are expressed as follows:

$$E_{\chi}(0,y) = \frac{c_{ox}}{\varepsilon_s} [\Psi_s(y) - \Psi_G]$$

(3c)

$$E_x(t_s, y) = \frac{c_{ox}}{\varepsilon_s} [\Psi_G - \Psi_b(y)]$$

(3d)

where  $C_{ox}$  demonstrates the oxide capacitances at each region, which is  $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$  in the R2 region. In this analytical model, the fringing fields effect is approximated by the conformal mapping techniques in R1 and R3 regions and is considered as  $C_{ox} = \frac{2}{\pi} \times \frac{\varepsilon_{ox}}{t_{ox}}$  (19). The gate potential is demonstrated as  $\Psi_G$ , where  $\Psi_G = V_{GS} - \phi_m + \chi + E_g/2$ ,  $\chi$  is the electron affinity of silicon,  $E_g$  is the energy bandgap of silicon, and  $\phi_m$  is work function of the gate metal.

By applying boundary conditions, coefficients  $a_0(y)$ ,  $a_1(y)$  and  $a_2(y)$  are calculated as functions of the surface potential  $\Psi_{\varsigma}(y)$ :

$$a_0(y) = \Psi_s(y) \tag{4a}$$

$$a_1(y) = \frac{c_{ox}}{\varepsilon_s} (\Psi_s(y) - \Psi_G$$

(4b)

$$a_2(y) = \frac{c_{ox}}{\varepsilon_s t_s} (\Psi_G - \Psi_S(y))$$

(4c)

By substituting coefficients 4 in Equation 2, the twodimensional Poisson equation becomes a second-order one-dimensional linear differential equation written as follows:

$$\Psi_s''(y) - 2\frac{c_{ox}}{\varepsilon_s t_s} \Psi_s(y) = -2\frac{c_{ox}}{\varepsilon_s t_s} \Psi_G - \frac{qN_s}{\varepsilon_s}$$

(5)

This equation can be written for three regions as:

$$\Psi_{s,i}^{"}(y) - k_i^2 \Psi_{s,i}(y) = -k_i^2 \Psi_{d,i}$$

(6)

$$k_i = (2\frac{c_{ox}}{\varepsilon_{ct}})^{0.5} \tag{7}$$

where i=1, 2 and 3 denote R1, R2 and R3 regions and  $k_i$  and  $\Psi_{di}$  are coefficient values in i-th region. The parameter  $\Psi_{d,i}$  is equal to the solution of one-dimensional Poisson equation (long-channel approximation), and is expressed as Equation 8 for i=2, 3.

$$\Psi_{d,i} = \Psi_G + \frac{qN_s t_s}{2C_{ox}} \tag{8}$$

and for i=1 as expression 9.

$$\Psi_{d,i} = \Psi_G - \frac{qN_s t_s}{2C_{ox}} \tag{9}$$

$k_i$  indicates reverse decay lengths or the characteristic lengths of the surface potential in each region. According

to Equation 7,  $k_i$  is not a function of  $V_{GS}$ . Finally, the general solution of 2D potential in Equation 6 for the surface potential is obtained. The surface potential in region  $R_i$  ( $y \in [y_i, y_{i-1}]$ ) is obtained as follows:

$$\Psi_{si}(y) = b_i e^{k_i (y - y_{i-1})} + c_i e^{-k_i (y - y_{i-1})} + \Psi_{di}$$

(10)

To obtain the coefficients  $b_i$  and  $c_i$  in Equation 10, suitable boundary conditions are considered at the  $R_1/R_2$  and  $R_2/R_3$  boundaries, which indicate continuity of potential and electric displacement.

$$b_{i} = \frac{1}{2 \sinh k_{i} L_{i}} \left( -\Psi_{di} (1 - e^{-k_{i} L_{i}}) - \Psi_{i-1} e^{-k_{i} L_{i}} + \Psi_{i} \right)$$

$$(11)$$

$$c_i = \frac{1}{2 \sinh k_i L_i} (+ \Psi_{di} (1 - e^{k_i L_i}) + \Psi_{i-1} e^{k_i L_i} - \Psi_i)$$

(12)

In Equations 11 and 12  $L_i = y_i - y_{i-1}$  for i = 1, 2, 3 and the terms  $\Psi_i$  and  $\Psi_{i-1}$  express potential values at the boundary of each region. According to these equations  $\Psi_{si}(y) = \Psi_i$ , using the following boundary conditions, the coefficients  $b_i$  and  $c_i$  are obtained (8):

$$\Psi_0 = b_1 + c_1 + \Psi_{d,1} \tag{13a}$$

$$\Psi_1 = b_1 e^{k_1 L_1} + c_1 e^{-k_1 L_1} + \Psi_{d,1} = b_2 + c_2 + \Psi_{d,2}$$

(13b)

$$\Psi_2 = b_2 e^{k_2 L_2} + c_2 e^{-k_2 L_2} + \Psi_{d,2} = b_3 + c_3 + \Psi_{d,3}$$

(13c)

$$\Psi_3 = b_3 e^{k_3 L_3} + c_3 e^{-k_3 L_3} + \Psi_{d,3} \tag{13d}$$

The surface potential values at the source end and at the drain end are  $\Psi_0$  and  $\Psi_3$ , respectively.

$$\Psi_0 = -\nu_t \ln \frac{N_1}{n_i} \tag{14}$$

$$\Psi_3 = V_D + v_t \ln \frac{N_3}{n_i} \tag{15}$$

where  $V_D$  demonstrates the drain voltage,  $v_t$  is the thermal voltage  $v_t = {kT}/{q}$  and the  $n_i$  represent the intrinsic carrier concentration.

# 3. 2. The Effect of Channel Mobile Charges and the Drain Voltage In this section, the mobile charges are considered to obtain an accurate analytical model for the potential. To consider the effect of channel mobile charges, the new mid-surface potential and the new inverse decay length are obtained as follows:

$$\Psi_{d,2new} = \frac{1}{2} \left( \Psi_{d,2} + \Psi_{\tau} - \sqrt{(\Psi_{d,2} - \Psi_{\tau})^2 + \delta^2} \right)$$

(16)

where  $\Psi_{d,2}$  is the mid-surface potential that does not include the effect of mobile charges.  $\Psi_{\tau}$  is given below where  $\alpha$  and  $\beta$  are the fitting parameters.  $\delta$  and  $N_{tran}$  are considered as:  $\delta = 0.04$  and  $N_{tran} = 10^{14}$  cm<sup>-3</sup> (16).

$$\Psi_{\tau} = V_D + \varphi + \alpha (\Psi_{d,2} - V_D - \varphi) + \beta (\Psi_{d,2} - V_D - \varphi)^2$$

$$(17)$$

$$\varphi = v_t \ln \frac{N_2 N_{tran}}{n_i^2} \tag{18}$$

The effect of mobile charges on the reverse decay length in the channel  $(k_2)$  is modeled as follows:

$$k_2 = \sqrt{2 \frac{c_{ox}}{\varepsilon_{si} t_{si}} - \frac{\sigma N_{inv}}{\varepsilon_{si} t_{si} (\Psi_0 - \Psi_{d,2})}}$$

(19)

$N_{inv} = 2C_{ox}(\Psi_g - \Psi_{d,2})$  represents the inversion charge in the channel and  $\sigma$  is a fitting parameter,  $1 < \sigma < 2$ .

To accurately model the potential in short channel devices, it is important to consider the impact of high drain voltages. These voltages lead to the formation of an inversion layer in the channel, which affects the potential distribution. Therefore, to enhance the accuracy of the model, the new gate potential  $\Psi_{G,eff}$  is used instead of  $\Psi_G$  (7), where  $\alpha=0.6$  and  $\theta_t=0.1$  are fitting parameters.

$$\begin{split} \Psi_{G,eff} &= \Psi_G - \alpha \theta_t \ln[1 + \exp\left(\frac{\Psi_G - \Psi_3}{\theta_t}\right)] + \\ \alpha \theta_t \ln[1 + \exp\left(\frac{\Psi_0 - \Psi_G}{\theta_t}\right)] \end{split} \tag{20}$$

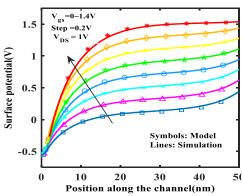

Figure 2, shows the front surface potential along the lateral distance in y-axis at different gate voltages. Obviously, as the gate voltage increases, the potential in the channel region increases. With increasing the gate voltage, the mobile charges accumulate at the channel surface below the gate and gradually an inversion layer is formed; consequently, the channel potential connects to the drain Fermi level, and becomes almost independent of the gate voltage. In addition, by increasing inversion charges, drain depletion region would gradually become smaller; thus, the source depletion region would increase.

## **3. 3. Modified Surface Potential** In the parabolic approximation method used in literature to solve the 2-D Poisson equation, surface potential is usually obtained and tunneling current is computed based on surface potential (15, 16, 18). Although these analytical models

**Figure 2.** The front surface potential distribution obtained from simulation (line) and analytical model (symbol) at gate voltages from  $V_q = 0V$  to  $V_q = 1.4V$  in steps of 0.2 V

can predict the surface potential accurately, the model cannot predict the potential profile in the channel depth.

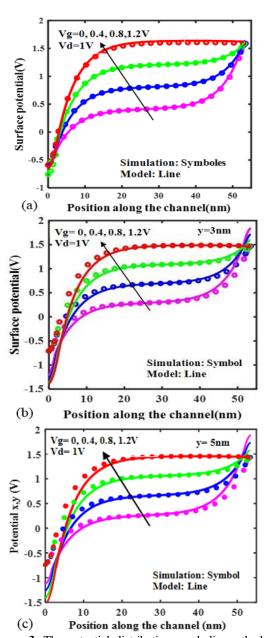

The validation of the surface potential distribution behavior of the model against the TCAD simulation results on the surface and at the different depths of the channel for  $V_g = 0, 0.4, 0.8, 1.2 V$  and  $V_d = 1V$  are depicted in Figure 3.

The potential distribution is shown inside the channel at different depths inclusive the surface of the channel, 3 nm below the surface, 5 nm below the surface in the center of the channel without considering the modified surface potential.

Figure 3a, shows the surface potential, Figure 3b, shows the potential distribution at 3 nm below the surface in (y = 3nm) and Figure 3c, depicts the potential distribution, 5 nm beneath the surface (center of the channel, y = 5nm). Note that the semiconductor thickness is 10 nm.

The analytical model well captures the effect of the mobile charges and effect of the drain voltage. Accuracy of the simulation results and analytical model can be simply seen in Figure 3a, while the model results are not consistent with the TCAD simulation data at the depth of 3 nm and 5 nm in Figures 3b and 3c.

In the parabolic approximation method, in fact, the potential is resolved along the path where the current dominates (along the oxide-semiconductor junction); hence, the accuracy of this method is just well along this path while close to the center of the channel, the accuracy decreases.

To achieve 2D potential distribution correctly, Equation 2 is used to convert the 2-D Poisson equation into a second-order one-dimensional linear differential equation in terms of the surface potential. Unlike the models in literature (15, 16, 18) which use  $\frac{\partial^2 \Psi(x,y)}{\partial x^2}$  and  $\frac{\partial^2 \Psi(x,y)}{\partial y^2}$  at x=0 (surface) an equation for arbitrary x is derived which gives the potential distribution from the surface down to the channel depth. Equation 5 turns into the following equation to include x dependency.

$$-2\frac{\eta}{t_s^2}(\Psi_S(y) - \Psi_G) + \Psi_S''(y)\left[1 + \frac{\eta}{t_s}x - \frac{\eta}{t_s^2}x^2\right] = \frac{-qN_S}{\varepsilon_S}$$

(21)

where  $\eta = \frac{c_{ox}}{c_{si}}$  and for simplicity, A' is defined as  $A' = 1 + \frac{\eta}{t_s}x - \frac{\eta}{t_s^2}x^2$ ; therefore,

$$\Psi_s''(y) - \frac{1}{A'} \frac{2\eta}{t_s^2} \Psi_s(y) = -\frac{qN_s}{\varepsilon_s} \frac{1}{A'} - \frac{1}{A'} \frac{2\eta}{t_s^2} \Psi_G$$

(22)

By defining  $k_{i,new}^2 = \frac{1}{A'} \frac{2\eta}{t_s^2}$  and mid-potential  $\Psi_{di,new} = \frac{t_s^2}{2\eta} \left( \frac{qN_s}{\varepsilon_s} + \frac{2\eta}{t_s^2} \Psi_G \right)$ , the differential equation for all regions can be written in a closed form analytical expression for the surface potential as follows:

$$\Psi_{si}^{"}(y) - k_{i,\text{new}}^{2} \Psi_{si}(y) = -k_{i,\text{new}}^{2} \Psi_{di,\text{new}}$$

(23)

$$k_{i,new} = \sqrt{\frac{2\varepsilon_{ox}}{\varepsilon_{si}t_{ox}t_{si} + \varepsilon_{ox}t_{si}x - \varepsilon_{ox}x^2}}$$

(24)

**Figure 3.** The potential distribution parabolic method is compared with the simulation results. In (a) model shows excellent matching with simulation data in surface potential, here the effect of the mobile charges and effect of the drain voltage is included. (b) displays the potential distribution profile along the channel for 3 nm below the device surface for  $V_{ds} = 1 V$  and  $V_{gs} = 0V$  to 1.2 V in steps of 0.4 V and, (c) shows potential distribution in the center of the channel (y = 5nm). In the DG-TFET, by moving towards the center of the channel and away from the surface of the semiconductor, the match between the model and the semiconductor becomes less and the analytical model cannot predict the potential profile well

Equation 6 using new reverse decay length  $(k_{i,new})$  in Equation 24 has been modified to represent the potential distribution at any depth of the device.

The electric field is computed by differentiating electrostatic potential with respect to x and y coordinates in each region.

$$E_{yi} = -\frac{\partial \Psi(x, y)}{\partial y} = b_i k_i e^{k_i (y - y_{i-1})} - k_i c_i e^{-k_i (y - y_{i-1})}$$

(25)

$$E_{xi} = -\frac{\partial \Psi(x, y)}{\partial x} = a_1(y) + 2a_2(y)x$$

(26)

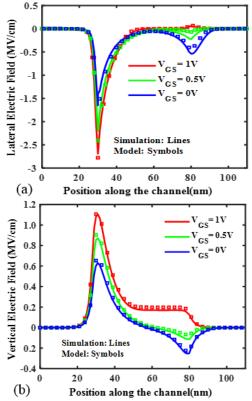

The electric field along the surface of the 2-D TFET in the x and y directions have been shows in Figure 4. As can be seen, the lateral electric field in the y direction is larger than the vertical electric field in the x direction at the source-channel interface. Hence, for simplicity in calculating the tunneling generation rate, the vertical field can be ignored. The length of the depletion regions on the source and drain sides is indicated by  $L_1$  and  $L_3$ , respectively, and are calculated as follows:

$$L_{1} = \sqrt{\frac{2\varepsilon_{s}(\Psi_{1} + \nu_{t} \ln \frac{N_{1}}{n_{i}})}{qN_{1}}}$$

(27)

**Figure 4.** (a)The lateral electric field, (b)the vertical electric field was obtained from the simulator (line) and the analytical model (symbol) at different gate voltages. The dielectric constant  $SiO_2$  is  $\varepsilon_{ox}=3.9$ , and the drain voltage is  $V_D=1V$

$$L_{3} = \sqrt{\frac{2\varepsilon_{s}(V_{D} + \nu_{t} \ln \frac{N_{3}}{n_{i}} - \Psi_{2})}{qN_{3}}}$$

(28)

$L_2$  is the channel length. Using the continuity of potential at the boundary of regions  $R_1/R_2$  and  $R_2/R_3$ , the depletion lengths can be calculated (16, 19).

## 4. ANALUTICAL MODEL FOR THE DRAIN CURRENT

The predominant current mechanism in TFETs is band-to-band tunneling (BTBT) current from the valance band of the source to the conduction band of the channel. In order to obtain the drain current, the amount of BTBT tunneling generation in Equation 30 must be integrated over the effective tunneling volume. The drain current is expressed as:

$$I_D = q \int_0^{t_{si}} \int_0^L \int_0^w G_{btbt} \, dx \, dy \, dz \tag{29}$$

The band-to-band generation rate ( $G_{BTBT}$ ) is taken from the Kane's model (20).

$$G_{BTBT} = A \frac{|E|^P}{\sqrt{E_g}} exp \left[ -B \frac{E_g^{3/2}}{|E|} \right]$$

(30)

In Equation 30, A and B are Kane's model parameters and are dependent on the material, the semiconductor energy gap and the effective mass of the carriers (10, 15, 16, 18). |E| represents electric field amplitude  $|E| = \sqrt{E_x^2 + E_y^2}$ . In a heterojunction,  $E_{g,eff}$  is used as the effective bandgap, and is usually determined from the bandgaps of the bulk and electron affinities materials.  $E_{g,eff} = E_{g2} - \Delta E_V$  and  $\Delta E_V = (\chi_2 - \chi_1) + (E_{g2} - E_{g1})$ .

$\Delta E_V$  is the off-set between the valance bands of the two materials (18). BTBT generation rate is dependent on the electric field at each point. Integrating  $G_{BTBT}$  in Equation 29 is the main challenge in TFET analytical modeling. Equation 29 cannot be computed analytically; therefore, several methods have been proposed in the literature for approximating this integral, in which accuracy is a challenge. The integral solution method in these papers (21, 22) is based on the exponential dependence of the  $G_{BTBT}$  on the electric field and considering the average electric field ( $E_{avg}$ ) in the minimum tunneling length ( $l_{tun_{min}}$ ). In this paper, to calculate this integral, the tangent line approximation method is used (9-11).

## 4. 1. Tunneling Generation Rate in the Channel

In the tangent line approximation (TLA) method,  $G_{BTBT}$  curve is considered along the channel length, and the tangent lines on the curve are drawn to intersect the horizontal axis and form triangles. The sum of these triangular areas gives the beneath area of the  $G_{BTBT}$  curve, which is the integral of the tunneling value.

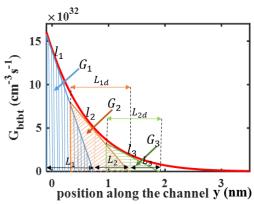

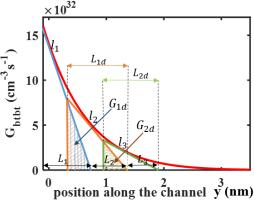

At the source-channel interface,  $G_{BTBT}$  has the highest value, and along the channel it reduces steeply to a negligible amount. In Figure 5,  $l_1$ ,  $l_2$  and  $l_3$  are tangent lines and the area under these lines can be expressed as  $G_1$ ,  $G_2$  and  $G_3$ , respectively. To simplify the method, at the source-channel junction y is assumed y = 0.

$$L_1 = \frac{G_{btbt}(0)}{G'_{btbt}(0)} \tag{31}$$

$$G_1 = \frac{1}{2} L_1 G_{btbt}(0) = \frac{1}{2} L_1^2 G'_{btbt}(0)$$

(32)

The slope of the tangent line  $l_1$  at y=0 is denoted as  $G'_{btbt}(0)$ .  $L_1$  is the length between y=0 and the y-intercept of  $l_1$ . Then, at  $y=L_1$ , the tangent line  $l_2$  is determined with the slope of  $G_{btbt}(y)$  to the point where it intersects the previous line  $l_1$ . The length between y-intercepts of  $l_1$  and  $l_2$  is called  $L_2$ .

$$L_2 = \frac{G_{btbt}(L_1)}{G'_{btbt}(L_1)} \tag{33}$$

$$G_2 = \frac{1}{2} L_{1d}^2 G'_{btbt}(L_1) \tag{34}$$

$$L_{1d} = \frac{G'_{btbt}(0) L_2}{G'_{btbt}(0) - G'_{btbt}(L_1)}$$

(35)

The  $L_{1d}$  expresses the distance between the intersection of line  $l_2$  on the y-axis and the intercept of  $l_1$  and  $l_2$  lines. This process is repeated and tangent line  $l_3$  is drawn from its y-intercept  $(L_1 + L_2)$  to the point it intersects the tangent line  $l_2$ .

$$L_3 = \frac{G_{btbt}(L_1 + L_2)}{G'_{btbt}(L_1 + L_2)} \tag{36}$$

$$G_3 = \frac{1}{2} L_{2d}^2 G'_{btbt} (L_1 + L_2)$$

(37)

$$L_{2d} = \frac{G'_{btbt}(L_1) L_3}{G'_{btbt}(L_1) - G'_{btbt}(L_1 + L_2)}$$

(38)

**Figure 5.** The band to band generation rate as a function of y along the channel length at  $V_{GS}=1.5V$  and  $V_{DS}=1V$ . The tangent lines  $l_1, l_2, l_3$  on the  $G_{btbt}$  curve and creating the triangular areas with the area  $G_1, G_2, G_3$ , respectivily; which can be regarded as the total area of the shaded regions

The  $G_{1d}$  represents the common area under the tangent lines  $l_1$  and  $l_2$ . Furthermore,  $G_{2d}$  is the common areas between tangent lines  $l_2$  and  $l_3$  as shown in Figure 6. The general expression are given in literature (9).

$$G_{1d} = \frac{1}{2} (L_{1d} - L_2)^2 G'_{btbt}(0)$$

(39)

$$G_{2d} = \frac{1}{2} (L_{2d} - L_3)^2 G'_{btbt}(L_1)$$

(40)

Finally, a closed-form equation for total  $G_{BTBT}$  is obtained using TLA method that gives  $\int G_{BTBT} dv = G_{total}$ . Final analytical expression is given in Equation 41.

$$\begin{aligned} G_{btbt\;channel} &= G_1 + G_2 + G_3 + \dots + G_n - \\ G_{1d} - G_{2d} - \dots - G_{n-1d} \end{aligned} \tag{41}$$

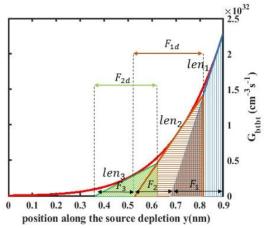

# **4. 2. Tunneling Generation Rate in the Source Depletion** To calculate the drain current accurately, the tunneling rate in the source depletion region should be calculated in addition to tunneling rate in the channel region. Figure 7 illustrates the tunneling rate in the source depletion region calculated by using the TLA method, which increases the accuracy of the model at high gate voltages.

$$\begin{aligned} G_{btbt\; source\; deplation} &= G_{1,sdep} + G_{2,sdep} + \cdots + \\ G_{n,sdep} &- G_{1d,sdep} - G_{2d,sdep} - \cdots - G_{n-1d,sdep} \end{aligned} \tag{42}$$

Considering both  $G_{btbt\ channel}$  and  $G_{btbt\ source\ deplation}$ , the total  $G_{BTBT}$  can be expressed as follows:

$$G_{BTBT \ total} = G_{btbt \ channel} + G_{btbt \ source \ deplation}$$

(43)

Thus, the drain current per unit width is calculated as follows:

$$I_D = q t_{si} G_{BTBT \ total} f_{fermi} \tag{44}$$

**Figure 6.** The tangent line approximation method for solving the integral of the tunneling value. The common area of the tangent lines  $l_1$  and  $l_2$  on the  $G_{btbt}$  curve and forming a triangular area with the area  $G_{1d}$ . Also  $G_{2d}$  is the common area under the tangent lines  $l_2$  and  $l_3$  on the  $G_{btbt}$  curve

**Figure 7.** The tunneling generation rate as a function of y along the source depletion region at  $V_{GS}=1.5V$  and  $V_{DS}=1V$ . The tangent lines  $len_1, len_2, len_3$  on the  $G_{btbt}$  curve and creating the triangular areas with the area  $G_{1,sdep}, G_{2,sdep}, G_{3,sdep}$  respectively. Common areas of the tangent lines  $len_1$  and  $len_2$ ,  $len_2$  and  $len_3$  on the  $G_{btbt}$  curve in the source depletion region forming a triangular area with the area  $G_{1d,sdep}$  and  $G_{2d,sdep}$  respectively

where  $f_{fermi}$  is a correction factor to insure  $I_{DS} = 0$  at  $V_{DS} = 0$  and  $\eta$  is an experimental coefficient (9, 19).

$$f_{fermi} = 1 - \frac{2}{\frac{V_{DS}}{(1+e^{\frac{V}{\eta}V_{E}})}} \tag{45}$$

## 5. MODEL VERIFICATION AND RESULTS

To verify the proposed model, in Figure 1, the investigated H-TFET is simulated with the ATLAS device simulator and is compared with the proposed analytical model. The device parameters used for simulation and analytical model are mentioned in Tables 1 and 3.

The BTBT generation rate in the source channel junction at the beginning of the channel is more than the amount of tunneling in the source depletion region, and in the calculations, the amount of tunneling in the channel region is dominant. With considering the amount of

tunneling in the source depletion region along with the channel region, the accuracy of drain current increases as are mentioned in Table 2. The accuracy can be improved by increasing the number of tangent lines. Accuracy of TLA method is reported in Table 2 for number of repetition steps. The accuracy 97.2% can be achieved by using eight tangent lines.

In this section, comparisons are made for a number of different biases, dielectric constants for oxide devices and different materials and mole fractions of material. For TFET and heterojunction TFET based on different material devices, parameters like bandgap, charge carriers tunneling masses, constants of Kane's model are adjusted.

In Table 3, parameters like charge carriers tunneling masses, intrinsic carrier concentration, permittivity and constants of Kane's model for TFET and H-TFETs based on different material devices are adjusted.

Here, a number of results from the proposed analytical model for the n-type DG-TFET structure as well as the double gate H-TFET structure are reviewed and evaluated. For this purpose, a different set of the results of proposed model are compared with simulation results with the calibrated numerical simulator.

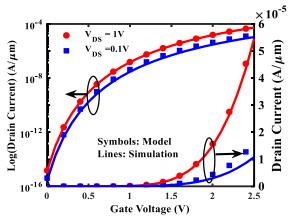

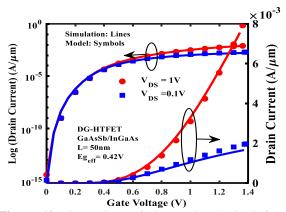

In Figure 8, the transfer characteristic  $(I_D - V_{GS})$  for a double-gate TFET with the specifications mentioned in Table 1 is drawn for the drain voltage  $V_{DS} = 1V$  and  $V_{DS} = 0.1~V$ . In this figure, the transition characteristic is drawn for both logarithmically and linearly. As can be seen from Figure 8, in a wide range of biases, the obtained results from our analytical model are consistent with the TCAD simulation results.

TABLE 2. Accuracy of TLA method

| Number of repetition steps | Accuracy<br>considering<br>channel | Accuracy considering<br>channel & source<br>depletion |

|----------------------------|------------------------------------|-------------------------------------------------------|

| 1                          | 53.95%                             | 60.95%                                                |

| 2                          | 83.04%                             | 85.48%                                                |

| 3                          | 92.52%                             | 93.41%                                                |

| 4                          | 95.66%                             | 96.02%                                                |

**TABLE 3.** BTBT model parameters

| Material                                    | Si SiGe                                              |                              | $GaAs_{0.5}Sb_{0.5}$                 | $In_{0.53}Ga_{0.47}As$ |  |

|---------------------------------------------|------------------------------------------------------|------------------------------|--------------------------------------|------------------------|--|

| me.tunnel(Kg)                               | $0.322  m_0$                                         | $0.322 m_0$ $0.328 m_0$ $0.$ |                                      | $0.0332 \ m_0$         |  |

| mh.tunnel(Kg)                               | $0.549 \ m_0$ $0.549 \ m_0$                          |                              | $0.421 \ m_0$ 0.471 m                |                        |  |

| Intrinsic carrier concentration $(ni)$      | $1.45 \times 10^{10}$                                | $2.86 \times 10^{12}$        | $1.37 \times 10^{12}$                | $7.62 \times 10^{11}$  |  |

| Permittivity ( $oldsymbol{arepsilon}_{r}$ ) | $3.9 \ \varepsilon_0$                                | $13.9 \ \varepsilon_0$       | $14.3 \ \varepsilon_0$               | $13.9 \ \varepsilon_0$ |  |

| Material TFET                               | $A_{BTBT}$ (eV <sup>1/2</sup> /cm.s.V <sup>2</sup> ) |                              | $B_{BTBT}$ (V/cm.eV <sup>3/2</sup> ) |                        |  |

| Si                                          | $3.5 \times 10^{21}$                                 |                              | 22.5×10 <sup>6</sup>                 |                        |  |

| SiGe/Si                                     | 4.1×                                                 | $10^{22}$                    | $2.45 \times 10^{7}$                 |                        |  |

| GaAsSb/InGaAs                               | 1.3×                                                 | $10^{20}$                    | $6.3 \times 10^6$                    |                        |  |

**Figure 8.** Comparison of the results obtained from (Lines) simulations and (symbols) our model for the transfer characteristic DG-TFET based on Si for different drain voltages as Logarithmically and linearly

In the TFET based on the hetero dielectric and the hetero structure, different materials from groups III-V with group IV are used to increase the performance of H-TFET (23-25). In the analytical models, the effect of using materials with hetero structure is considered in addition to the tunneling phenomenon to the appropriate placement of the valance and conduction bands in the TFET, and an effective bandgap  $E_{g,eff}$  is defined for the model (10, 18).

In the heterojunction (n-type) TFET, the use of low bandgap materials at the source side along with a lower tunneling mass causes more overlap between the energy bands at the channel-source junction and smaller the tunneling distance. As a result, the on-state current increases (26).

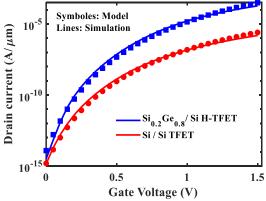

The comparison between switching performance of homojunction TFET and double gate H-TFET using  $\mathrm{Si}_{0.2}\mathrm{Ge}_{0.8}$ in the source and Si in the channel and drain regions is shown in Figure 9.

**Figure 9.** Transfer characteristics of homojunction TFET and H-TFETs predicted by the TCAD simulators (line) and analytical models (symbol)

As expected, for the same gate voltage range, H-TFET structure provide more  $I_{ON}$  current than homojunction TFET structure, and our proposed analytical model can follow the simulation curve well.

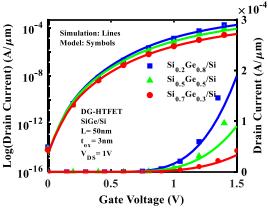

In Figure 10, the transfer characteristics of three double gate H-TFETs based on different molar ratio of  $\mathrm{Si}_{(1-x)}\mathrm{Ge}_x$  are shown. As the results of simulation and analytical model are shown,  $\mathrm{Si}_{0.2}\mathrm{Ge}_{0.8}$  has more current than the other two structures. The reason is the smaller energy gap in the source region and the more energy band bending at the tunneling region of  $\mathrm{Si}_{0.2}\mathrm{Ge}_{0.8}$  compared to  $\mathrm{Si}_{0.5}\mathrm{Ge}_{0.5}$  and  $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$  structures.

Mostefai (27) studied on energy gap (Eg) as a function of different composition x and y in  $Ga_x In_{1-x} As_y Sb_{1-y}$  at T = 300 K and intrinsic carrier concentration (ni) as a function of temperature and effective density of states  $N_c$  and  $N_v$  in the conduction band and valence band, respectively. So far several articles worked on  $GaAs_{1-y}Sb_y$  and  $In_{1-x}Ga_xAs$  (10, 28, 29). The effective energy bandgap  $(E_{q,eff})$  for heterojunction TFET is an important design parameter. Although there is no definite value for  $E_{g,eff}$  in the  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$ . Various ranges of effective bandgap can be seen in the literature (30, 31). With comparing measured  $I_D - V_{GS}$  curve for the  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$ H-TFET, 0.42eV is more suitable (31).

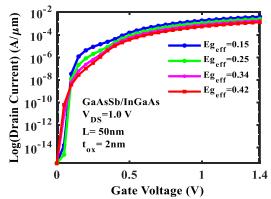

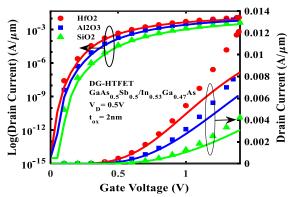

For best matching between the results of the TCAD simulator and the results of the analytical model. Figure 11 shows transfer characteristics  $I_D - V_{GS}$  for different  $E_{g,eff}$  in  $V_{DS} = 1V$  and dielectric constant  $Al_2O_3$  ( $\varepsilon_{ox} = 8.5$ ). Parameters mentioned in Table 2 are accounted for GaAsSb/InGaAs and its results are compared with simulation results.

In Figure 12, the effect of drain-source voltages on transfer characteristic of a DG-HTFET  $GaAs_{0.5}Sb_{0.5}/$

**Figure 10.**  $I_D - V_{GS}$  curve obtained for  $\mathrm{Si}_{(1-\mathrm{x})}\mathrm{Ge}_\mathrm{x}$  /Si/Si H-TFET for molar ratios X= 0.3, 0.5, 0.8, where the simulations are shown as lines and the analytical model is shown as symbols

**Figure 11.** The transfer characteristics of  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$  for several effective energy bandgap ( $E_{g,eff}$ ). our model predicted by TCAD simulations (lines) and by the analytical model (symbols)

**Figure 12.** Comparison of the results obtained from simulations (Lines) and our model (symbols) for the transfer characteristic DG-HTFET based on  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$  for various drain voltage ( $V_{DS}=1V$ ) and ( $V_{DS}=0.1V$ ) as Logarithmically and linearly

$In_{0.53}Ga_{0.47}As$  for  $V_{DS}=1V$  and  $V_{DS}=0.1V$  is shown. In short channel devices, the applied drain-source voltage affects the distance of tunneling path. As can be seen in Figure 12, it modulates the  $I_{ON}$  reasonably while the subthreshold swing remains almost unchanged.

Theresults obtained from our analytical model are consistent with the TCAD simulator and shows that the model predicts accurately.

To reduce power density and better switching performance, TFETs are considered in low power applications (32-34). Figure 13, shows the log  $I_D - V_{GS}$  curves of a  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$  DG-HTFET for different dielectric constants.

The channel length and other device parameters are the same. Thin oxides with high permittivity lead to a greater oxide capacitance, and provides higher charge being formed in the channel at the same gate voltage, which results in a higher control of the gate on the electrostatics of the channel. This makes higher  $I_{ON}$  and lower bias voltages. As expected from Figure 13,  $HfO_2$  provides more current at the same rang of gate voltages and our analytical model are consistent with the TCAD results.

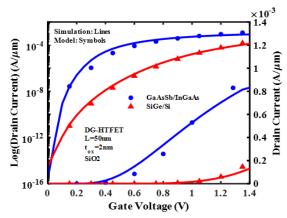

Table 4, shows comparative analysis of the proposed H-TFET structural parameters with existing literature. Transfer characteristics of DG-HTFET for two different heterojunctions, *SiGe/Si* and *GaAsSb/InGaAs*, are shown in Figure 14, by considering TCAD simulations (Lines) and analytical model (symbols). The parameters

**Figure 13.**  $I_D - V_{GS}$  curves obtained of the DG-HTFET  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$  from simulation (lines) and our model (symbols) for different dielectric constant material, HfO<sub>2</sub> ( $\varepsilon_{OX} = 22$ ), Al<sub>2</sub>O<sub>3</sub> ( $\varepsilon_{OX} = 8.5$ ) and SiO<sub>2</sub> ( $\varepsilon_{OX} = 3.9$ )

**TABLE 4.** The comparative H-TFET with existing literature

|            | Source | Channel | Eot (nm) | Oxide            | $I_{ON}(A/\mu m)$ | $I_{OFF}\left(A/\mu m\right)$ | SS (mV/dec) |

|------------|--------|---------|----------|------------------|-------------------|-------------------------------|-------------|

| (9)        | GaAsSb | InGaAs  | 2        | SiO <sub>2</sub> | 10-6              | 10-13                         | 45          |

| (30)       | SiGe   | Si      | 2        | $HfO_2$          | 10-3              | $10^{-13}$                    | 60          |

| (30)       | InGaAs | InP     | 2        | $SiO_2$          | 10-8              | $10^{-17}$                    | 80          |

| (21)       | InGaAs | InP     | 2        | $SiO_2$          | 10 <sup>-5</sup>  | $10^{-13}$                    | 80          |

| (26)       | Si     | Si      | 2        | $SiO_2$          | 10 <sup>-4</sup>  | $10^{-15}$                    | 55          |

| This paper | SiGe   | Si      | 3        | $SiO_2$          | 10 <sup>-4</sup>  | $10^{-15}$                    | 50          |

| This paper | GaAsSb | InGaAs  | 2        | $SiO_2$          | 10-2              | $10^{-16}$                    | 30          |

**Figure 14.** Transfer characteristics of the H-TFET  $Si_{0.2}Ge_{0.8}/Si$  and  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$  predicted by the TCAD simulators (line) and analytical models (symbol)

in Table 2 are considered for both numerical simulation and analytical model. The  $GaAs_{0.5}Sb_{0.5}/In_{0.53}Ga_{0.47}As$  has higher current than the  $Si_{0.2}Ge_{0.8}$ . According to Figure 14, matching the results of proposed model and the numerical simulations confirm the validity of the model.

## 6. CONCLUSIONS

In this paper, a universal physics-based analytical model for DG H-TFETs is proposed which accurately predicts the potential and the drain current. The fringing fields and effects of mobile charges on the reverse decay length in the channel are considered. The effect of high drain voltages on the potential, using new gate potential  $\Psi_{G,eff}$ , is introduced, as well. The model consists of a complete 2D expression for the potential profile to predict the potential distribution in the channel depth in addition to the surface of the device. The mid-potential  $\Psi_{di,new}$  and new reverse decay length  $k_{i,new}$  are modified to represent the potential distribution at any depth of the device. For drain current modeling, the effect of the extended depletion region in the source side is considered in TLA method, and  $G_{BTBT}$  is calculated in the channel and the source depletion region, which improves the accuracy of the model at high gate voltages by 97.2%. The proposed model is compared with TCAD results for different material and device parameters, which confirms the accuracy of the proposed analytical model.

## 7. REFERENCES

Maity N, Maity R, Baishya S. An analytical model for the surface potential and threshold voltage of a double-gate heterojunction

- tunnel FinFET. Journal of computational electronics.  $2019;18:65-75.\ 10.1007/s10825-018-1279-5$

- Pan A, Chui CO. A quasi-analytical model for double-gate tunneling field-effect transistors. IEEE electron device letters. 2012;33(10):1468-70. 10.1109/LED.2012.2208933

- Abdulwahid AH. Artificial intelligence-based control techniques for hvdc systems. Emerging Science Journal. 2023;7(2):643-53. 10.28991/ESJ-2023-07-02-024

- Divayana DGH, Suyasa PWA, Santiyadnya N, Andayani MSL, Sundayana IM, Astawa IND, et al. Utilization of the Weighted Product-Based CIPP Evaluation Model in Determining the Best Online Platform. HighTech and Innovation Journal. 2023;4(1):233-48. 10.28991/HIJ-2023-04-01-0155

- Zhang L, Chan M. SPICE modeling of double-gate tunnel-FETs including channel transports. IEEE Transactions on Electron Devices. 2014;61(2):300-7. 10.1109/TED.2013.2

- Graef M, Holtij T, Hain F, Kloes A, Iniguez B. A 2D closed form model for the electrostatics in hetero-junction double-gate tunnel-FETs for calculation of band-to-band tunneling current. Microelectronics Journal. 2014;45(9):1144-53. 10.1016/j.mejo.2014.04.033

- Horst F, Graef M, Hosenfeld F, Farokhnejad A, Hain F, Luong GV, et al., editors. Implementation of a DC compact model for double-gate Tunnel-FET based on 2D calculations and application in circuit simulation. 2016 46th European Solid-State Device Research Conference (ESSDERC); 2016: IEEE. 10.1109 /ESSDERC.2016.7599684

- Dutta R, Sarkar SK. Analytical modeling and simulation-based optimization of broken gate TFET structure for low power applications. IEEE transactions on electron devices. 2019;66(8):3513-20. 10.1109/TED.2019.2925109

- Devi WV, Bhowmick B, Pukhrambam PD. N+ pocket-doped vertical TFET for enhanced sensitivity in biosensing applications: modeling and simulation. IEEE Transactions on Electron Devices. 2020;67(5):2133-9. 10.1109/TED.2020.2981303

- Vishnoi R, Kumar MJ. An accurate compact analytical model for the drain current of a TFET from subthreshold to strong inversion. IEEE Transactions on Electron Devices. 2015;62(2):478-84. 10.1109/TED.2014.2381560

- Guan Y, Li Z, Zhang W, Zhang Y, Liang F. An analytical model of gate-all-around heterojunction tunneling FET. IEEE Transactions on Electron Devices. 2018;65(2):776-82. 10.1109/TED.2017.2783911

- Kumar S, Singh K, Baral K, Singh PK, Jit S. 2-D analytical model for electrical characteristics of dual metal heterogeneous gate dielectric double-gate TFETs with localized interface charges. Silicon. 2021;13:2519-27. 10.1007/s12633-020-00564-5

- Gholizadeh M, Hosseini SE. A 2-D analytical model for doublegate tunnel FETs. IEEE Transactions on Electron Devices. 2014;61(5):1494-500. 10.1109/TED.2014.2313037

- Ponnian J, Pari S, Ramadass U, Ooi CP. A Unified Power-Delay Model for GDI Library Cell Created Using New Mux Based Signal Connectivity Algorithm. Emerging Science Journal. 2023;7(4):1364-94. 10.28991/ESJ-2023-07-04022

- Bardon MG, Neves HP, Puers R, Van Hoof C. Pseudo-twodimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Transactions on Electron Devices. 2010;57(4):827-34. 10.1109/TED.2010.2040661

- Jain P, Yadav C, Agarwal A, Chauhan YS. Surface potential based modeling of charge, current, and capacitances in DGTFET including mobile channel charge and ambipolar behaviour. Solid-State Electronics. 2017;134:74-81. 10.1016/j.sse.2017.05.012

- Keighobadi D, Mohammadi S. Physical and analytical modeling of drain current of double-gate heterostructure tunnel FETs.

- Semiconductor Science and Technology. 2018;34(1):015009. 10.1088/1361-6641/aaeeeb

- Kaur S, Raman A, Sarin RK. Analytical modeling of surface potential, capacitance and drain current of heterojunction TFET. Applied Physics A. 2020;126:1-11. 10.1007/s00339-020-03945-0

- Lin S, Kuo J. Modeling the fringing electric field effect on the threshold voltage of FD SOI nMOS devices with the LDD/sidewall oxide spacer structure. IEEE Transactions on Electron Devices. 2003;50(12):2559-64. 10.1109/TED.2003.816910

- Kane E. Zener tunneling in semiconductors. Journal of Physics and Chemistry of Solids. 1960;12(2):181-8. 10.1016/0022-3697(60)90035-4

- Mohammadi S, Keighobadi D. A universal analytical potential model for double-gate Heterostructure tunnel FETs. IEEE Transactions on Electron Devices. 2019;66(3):1605-12. 10.1109/TED.2019.2895277

- Ranjith R, Suja K, Komaragiri RS. An analytical model for a TFET with an n-doped channel operating in accumulation and inversion modes. Journal of Computational Electronics. 2021;20:1125-36. 10.1007/s10825-021-01683-x

- Howldar S, Balaji B, Srinivasa Rao K. Design and Analysis of Hetero Dielectric Dual Material Gate Underlap Spacer Tunnel Field Effect Transistor. International Journal of Engineering, Transactions C: Aspects. 2023;36(12):2137-44. 10.5829/ije.2023.36.12c.01

- Howldar S, Balaji B, Srinivasa Rao K. Design and qualitative analysis of hetero dielectric tunnel field effect transistor device. International Journal of Engineering, Transactions C: Aspects. 2023;36(6):1129-35. 10.5829/ije.2023.36.06c.11

- Keighobadi D, Mohammadi S, Fathipour M. An analytical drain current model for the cylindrical channel gate-all-around heterojunction tunnel FETs. IEEE Transactions on Electron Devices. 2019;66(8):3646-51. 10.1109/TED.2019.2922232

- Dong Y, Zhang L, Li X, Lin X, Chan M. A compact model for double-gate heterojunction tunnel FETs. IEEE Transactions on

- Electron Devices. 2016;63(11):4506-13. 10.1109/TED.2016.2604001

- Mostefai A. Basic Characteristics of Gallium Indium Arsenide Antimonide (GaxIn1-xAsySb1-y) Semiconductors Using MATLAB. Journal of Nano-and Electronic Physics. 2022;14(4). 10.21272/jnep.14(4).04027

- Convertino C, Zota CB, Schmid H, Caimi D, Czornomaz L, Ionescu AM, et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. nature electronics. 2021;4(2):162-70. 10.1038/s41928-020-00531-3

- Arabhavi AM, Ciabattini F, Hamzeloui S, Flückiger R, Saranovac T, Han D, et al. InP/GaAsSb double heterojunction bipolar transistor emitter-fin technology with f MAX= 1.2 THz. IEEE Transactions on Electron Devices. 2022;69(4):2122-9. 10.1109/TED.2021.3138379

- Smets Q, Verhulst AS, El Kazzi S, Gundlach D, Richter CA, Mocuta A, et al. Calibration of the effective tunneling bandgap in GaAsSb/InGaAs for improved TFET performance prediction. IEEE transactions on electron devices. 2016;63(11):4248-54. 10.1109/TED.2016.2604860

- Detz H, Silvano de Sousa J, Leonhardt H, Klang P, Zederbauer T, Andrews AM, et al. InGaAs/GaAsSb based two-dimensional electron gases. Journal of Vacuum Science & Technology B. 2014;32(2). 10.1116/1.4863299

- Zare M, Peyravi F, Hosseini SE. Impact of hetero-dielectric ferroelectric gate stack on analog/RF performance of tunnel FET. Journal of Electronic Materials. 2020;49:5638-46. 10.1007/s11664-020-08315-3

- Ghosh S, Chattopadhyay A, Tewari S. Optimization of heterogate-dielectric tunnel FET for label-free detection and identification of biomolecules. IEEE transactions on Electron Devices. 2020;67(5):2157-64. 10.1109/TED.2020.2978499

- Arunkumar N, Senathipathi N, Dhanasekar S, Malin Bruntha P, Priya C. An ultra-low-power static random-access memory cell using tunneling field effect transistor. International Journal of Engineering, Transactions B: Applications. 2020;33(11):2215-21. 10.5829/ije.2020.33.11b.13

## COPYRIGHTS

©2024 The author(s). This is an open access article distributed under the terms of the Creative Commons Attribution (CC BY 4.0), which permits unrestricted use, distribution, and reproduction in any medium, as long as the original authors and source are cited. No permission is required from the authors or the publishers.

## Persian Abstract

چکیده

یک مدل تحلیلی دقیق برای جریان درین ترانزیستورهای تونلی ناهمگون، با در نظر گرفتن ناحیه تخلیه سورس، بارهای متحرک، و اثر ولتاژ درین ارائه شده است. این مدل با استفاده از روابط ریاضی جدید فرموله شده، توزیع پتانسیل را نه تنها در سطح، بلکه در عمق نیمه هادی به طور دقیق پیش بینی می کند. با استفاده از روش تقریب خط مماس با در نظر گرفتن ناحیه کانال و همچنین ناحیه تخلیه سورس، جریان تونل زنی باند به باند از ناحیه سورس به کانال به صورت تحلیلی و با استفاده از انتگرال مقدار تولید تونل زنی مدل کین محاسبه می شود. در مقایسه با نتایج شبیه سازی، مدل پیشنهادی دقت قابل توجهی در پیش بینی جریان درین دارد.